11、时序约束

1、时钟约束:

在xdc文件中添加语句

create_clock -period 20.000-name sys_clk -waveform {0.000 10.000} [get_ports sys_clk]

create_clock -period 20.000-name sys_clk -waveform {0.000 10.000} [get_ports sys_clk]

create_clock -period 100.000 -name clk [get_ports sys_clk_10MHz]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets sys_clk_10MHz]

时钟约束的作用是:有时使用板卡上的非时钟引脚作为时钟引脚时会报错,添加时钟约束之后可以解决这个问题。

2、时序约束

输入端到FPGA内部第一级触发器:set_input_delay

FPGA内部触发器之间:create_clock

FPGA内部末级触发器到输出端口:set_output_delay

FPGA输入端口到输出端口:set_max_delay

IO管脚约束---->指定管脚电平和位置

set_property IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

set_property PACKAGE_PIN N16 [get_ports sys_rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

set_property PACKAGE_PIN N16 [get_ports sys_rst_n]端接------

IO延迟约束

使用set_input_delay、set_output_delay来实现延迟约束,实际上这两个约束并不是调节数据的延迟,而是输入信号和输入时钟之间的延迟关系。

create_clock -name sysclk -period 10 [get_ports clkin]

set_input_delay 2 -max -clock sysclk [get_ports Datain]

set_input_delay 1 -min -clock sysclk [get_ports Datain]

create_clock -name sysclk -period 10 [get_ports clkin]

set_input_delay 2 -max -clock sysclk [get_ports Datain]

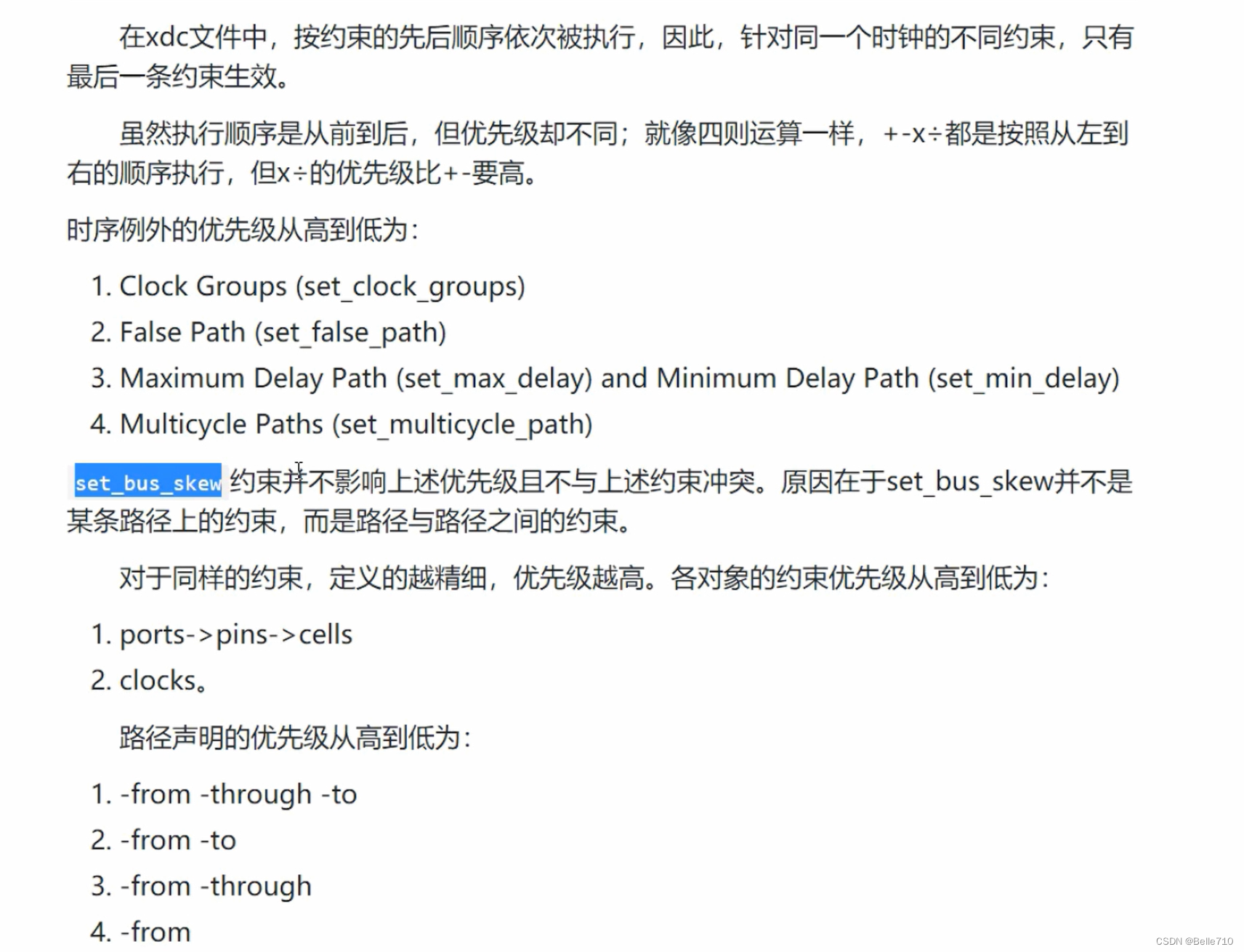

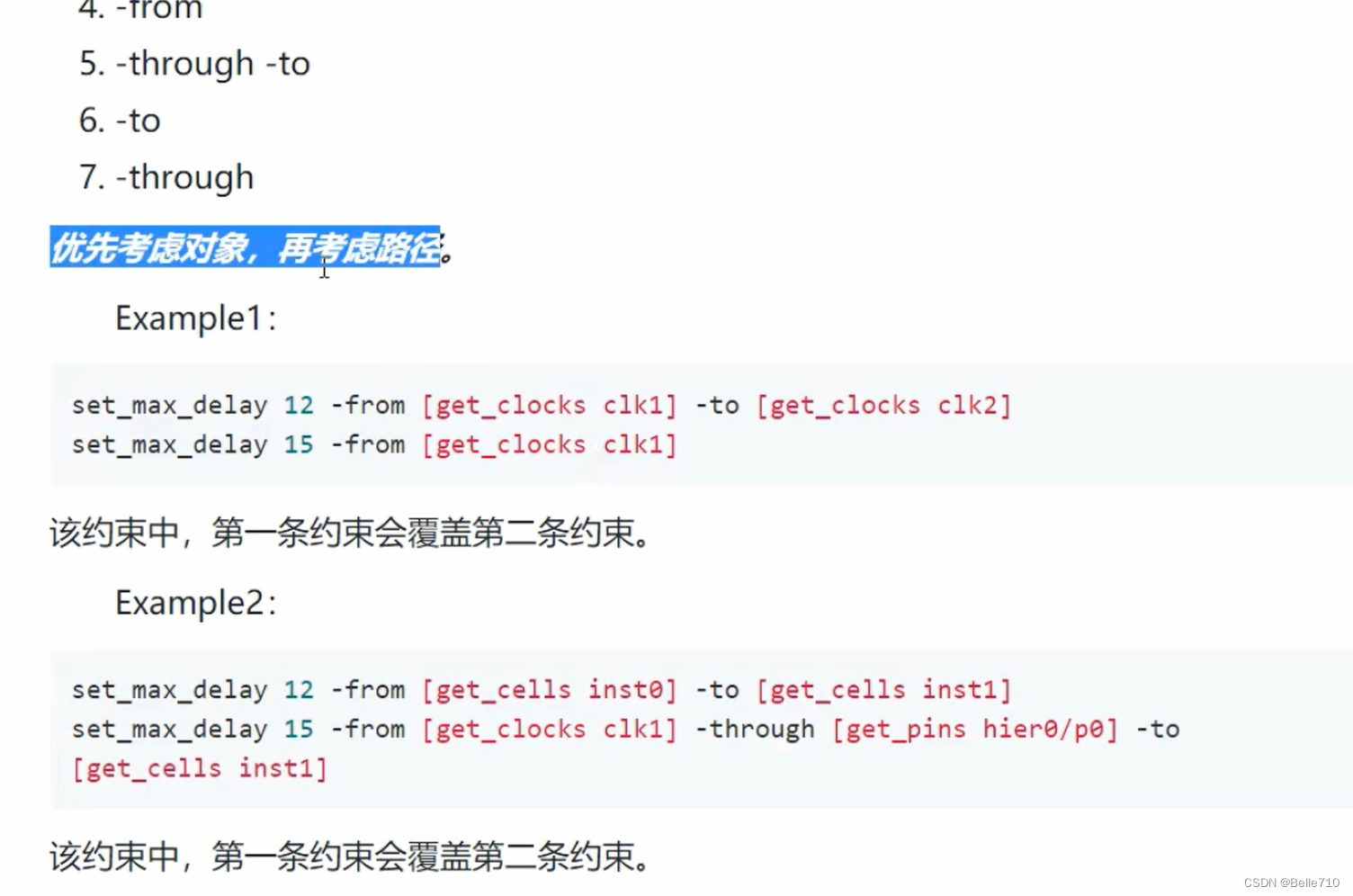

set_input_delay 1 -min -clock sysclk [get_ports Datain]3、xdc约束的优先级

xdc文件中,按约束先后顺序依次执行,因此如果对同一个时钟进行了多个约束,那么只有最后一条约束有效。

主时钟的创建

查看主时钟:

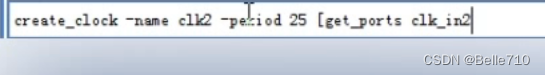

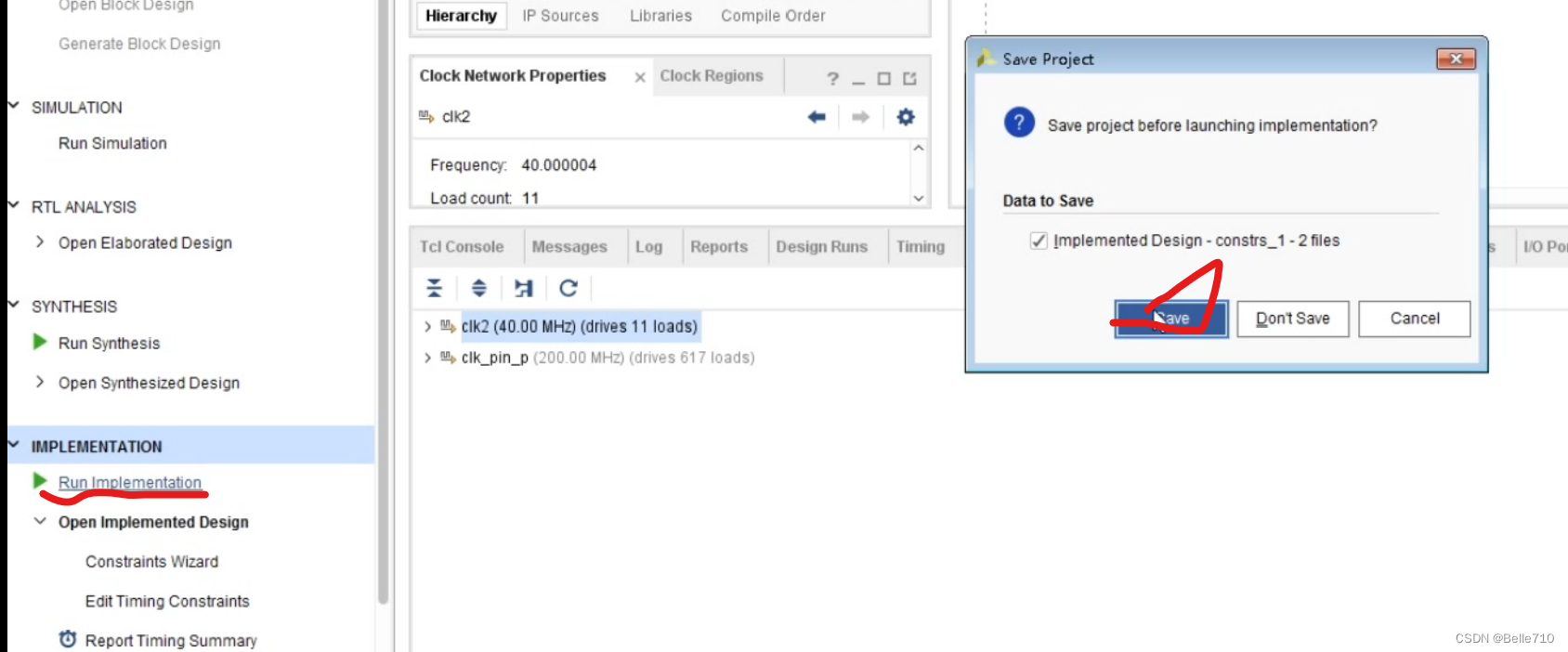

可以通过tcl命令直接创建时钟约束:(会自动写入时序约束文件中)

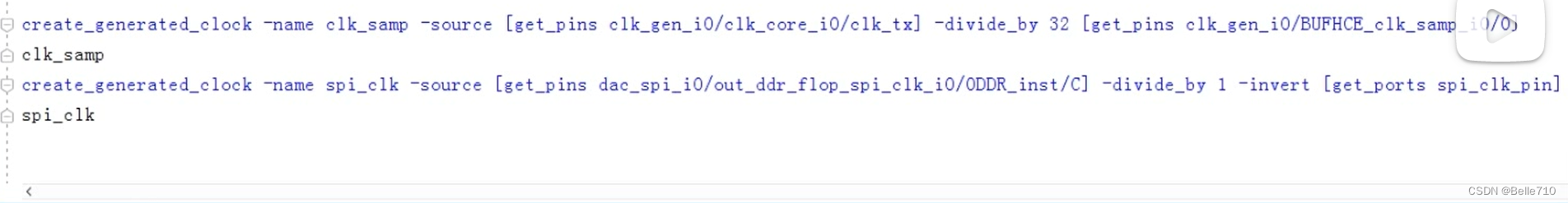

衍生时钟的创建